Prawa autorskie do tej instrukcji należą do Shenzhen Thinkcore Technology Co., Ltd. i wszelkie prawa są zastrzeżone. Żadne firmy ani osoby fizyczne nie mogą wyodrębniać części lub całości tej instrukcji, a osoby naruszające ją będą ścigane zgodnie z prawem.

Instrukcje sprzedawanej platformy programistycznej będą od czasu do czasu aktualizowane, należy pobrać najnowszą instrukcję ze strony internetowej www.think-core.com lub skontaktować się z przedstawicielem handlowym naszej firmy, nie będzie dalszych powiadomień.

|

Wersja |

Data |

Autor |

Opis |

|

Wersja 01 |

2022-08-04 |

|

Rewizja |

TC-RK3568 Podsumowanie płytki rozwojowej z otworem po pieczęci

Płytka rozwojowa TC-RK3568 z otworem na stempel zawiera TC-RK3568 SOM z otworem na stempel i płytkę nośną.

System TC-RK3568 Stamp Hole na module jest wyposażony w 64-bitowy procesor Rockchip RK3568, który jest skonfigurowany z dwurdzeniowym procesorem graficznym i wydajnym NPU.

RK3568, czterordzeniowy 64-bitowy procesor Cortex-A55, z procesem litograficznym 22 nm, ma częstotliwość do 2,0 GHz, zapewniając wydajną i stabilną wydajność przetwarzania danych sprzętu zaplecza. Istnieje wiele opcji przechowywania, co pozwala klientom na szybkie wdrożenie badań i produkcji produktów. Obsługuje do 8 GB pamięci RAM, o szerokości do 32 bitów i częstotliwości do 1600 MHz. Obsługuje wszystkie łącza danych ECC, dzięki czemu dane są bezpieczniejsze i bardziej niezawodne, a także spełnia wymagania uruchamiania aplikacji produktów o dużej pamięci. Jest zintegrowany z dwurdzeniowym procesorem graficznym, wysokowydajną jednostką VPU i wysokowydajną jednostką NPU. Karta graficzna obsługuje OpenGL ES3.2/2.0/1.1, Vulkan1.1. VPU może osiągnąć dekodowanie wideo 4K 60fps H.265/H.264/VP9 i kodowanie wideo 1080P 100fps H.265/H.264. NPU obsługuje przełączanie jednym kliknięciem popularnych frameworków, takich jak Caffe/TensorFlow.

Dzięki interfejsom wideo MIPI-CSI x2, MIPI-DSI x2, HDMI2.0, EDP może obsługiwać do trzech wyjść ekranowych z różnymi wyświetlaczami. Wbudowany 8M ISP obsługuje dwie kamery i HDR. Interfejs wejścia wideo można podłączyć do kamery zewnętrznej lub wielu kamer. Jest wyposażony w dwa adaptacyjne porty RJ45 Gigabit Ethernet, za pośrednictwem których można uzyskać dostęp do danych sieciowych wewnętrznych i zewnętrznych oraz je przesyłać, poprawiając wydajność transmisji sieciowej i spełniając potrzeby produktów z wieloma portami sieciowymi, takimi jak NVR i bramy przemysłowe.

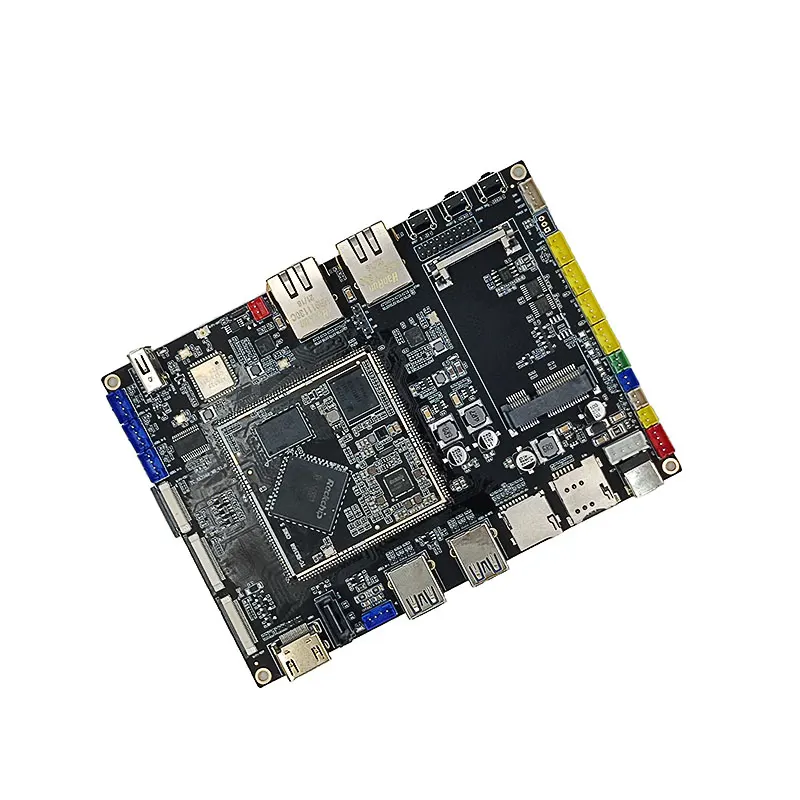

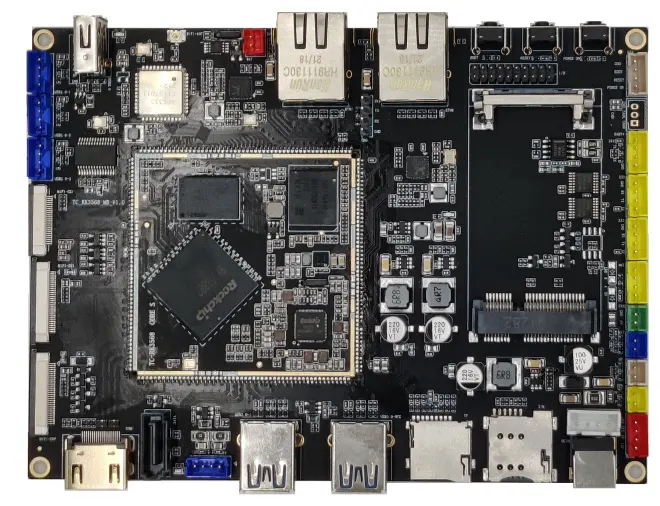

Płyta nośna zawiera wiele interfejsów, takich jak port 4G LTE, USB3.0, USB2.0, PCIE, dual Ethernet, WIFI, Bluetooth, wejście i wyjście Audio, wyjście HDMI, wyświetlacz MIPI DSI, wyświetlacz eDP, wyświetlacz LVDS, MIPI CSI kamera, gniazdo kart TF, RS485, RS232, TTL, CAN, wyjście zasilania, SATA itp.

Obsługiwane są systemy operacyjne Android 11, Ubuntu 18.04, Debian OS i Linux Buildroot. Stabilne i niezawodne działanie zapewnia bezpieczne i stabilne środowisko systemowe do badań i produkcji produktów.

Kompletny zestaw SDK, dokumenty programistyczne, przykłady, dokumenty technologiczne, samouczki i inne zasoby są udostępniane użytkownikom w celu dalszego dostosowania.

Rozmiar: 150mm x 110mm.

Bogate interfejsy mogą być bezpośrednio używane w różnych inteligentnych produktach, aby ułatwić ukończenie produktów.

Obsługiwane są systemy operacyjne Android 11.0, Ubuntu 18.04, Debian OS i Linux Buildroot.

Ta płyta może być szeroko stosowana w inteligentnych rejestratorach NVR, terminalach w chmurze, bramach IoT, sterowaniu przemysłowym, obliczeniach brzegowych, bramkach do rozpoznawania twarzy, serwerach NAS, konsolach środkowych pojazdów itp.

|

Specyfikacje |

|

|

procesor |

RockChip RK3568, czterordzeniowy 64-bitowy Cortex-A55, proces litograficzny 22 nm, częstotliwość do 2,0 GHz |

|

GPU |

RAMIĘ G52 2EE Obsługuje OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1 Wbudowany wysokowydajny sprzęt do akceleracji 2D |

|

NPU |

0.8Tops@INT8, zintegrowany wysokowydajny akcelerator AI RKNN NPU Obsługuje przełączanie jednym kliknięciem Caffe/TensorFlow/TFLite/ONNX/PyTorch/Keras/Darknet |

|

WPU |

Obsługuje dekodowanie wideo 4K 60fps H.265/H.264/VP9 Obsługuje kodowanie wideo 1080P 100fps H.265/H.264 Obsługuje 8M ISP, obsługuje HDR |

|

Baran |

2 GB/4 GB/8 GB |

|

Przechowywanie |

8 GB/16 GB/32 GB/64 GB/128 GB eMMC Obsługuje SATA 3.0 x 1 (rozszerzenie o 2,5-calowy dysk SSD/HDD) Obsługuje gniazdo kart TF x1 (rozwiń za pomocą karty TF) |

|

System operacyjny |

Android11/Linux Buildroot/Ubuntu/Debian |

|

Funkcje sprzętowe |

|

|

Wyświetlacz |

1 * HDMI2.0, obsługuje wyjście 4K przy 60 klatkach na sekundę 1 * MIPI DSI, obsługuje wyjście 1920*1080 przy 60 klatkach na sekundę 1 * LVDS, obsługuje wyjście 1920*1080 przy 60 klatkach na sekundę 1 * eDP1.3, obsługuje wyjście 2560x1600 przy 60 klatkach na sekundę |

|

Ethernet |

Obsługuje dwa porty Gigabit Ethernet (1000 Mb/s) |

|

Wi-Fi |

Mini PCIe do podłączenia 4G LTE Obsługuje Wi-Fi 6 (802.11 AX) Obsługuje BT5.0 |

|

PCIE3.0 |

Obsługuje interfejs PCE3.0 |

|

Audio |

1 * wyjście audio HDMI 1 * Wyjście głośnikowe 1 * Wyjście słuchawkowe 1 * Wbudowane wejście audio mikrofonu |

|

Kamera |

Obsługuje 1-kanałowy interfejs kamery MIPI-CSI Obsługuje HDR, obraz pozostaje wyraźny przy podświetleniu lub silnym oświetleniu

|

|

USB |

1 * Host USB3.0, 4 * Host USB 2.0, 1 * USB3.0 OTG |

|

SATA |

1 * SATA, 6,0 Gb/s |

|

Seryjny |

1 * TTL, 2 * RS232, 1 * RS485 |

|

MOGĄ |

Obsługa CAN2.0B, obsługa 1 mb/s, 8 mb/s |

|

Karta TF |

1 * gniazdo karty TF |

|

Inni |

GPIO i ADC |

|

Rozmiar |

150mm * 110mm |

|

|

|

|

Napięcie wejściowe |

12V/3A |

|

Temperatura przechowywania

|

-30 ~ 80 ° C |

|

temperatura robocza |

-20~60℃ |

|

Wilgotność przechowywania |

10%~80% |

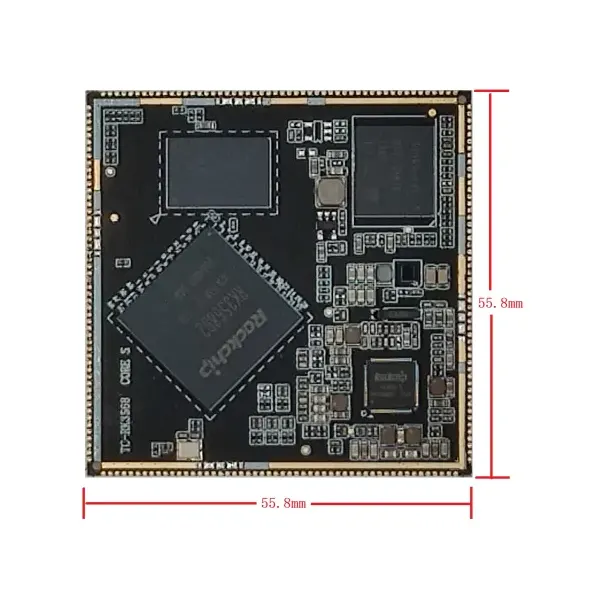

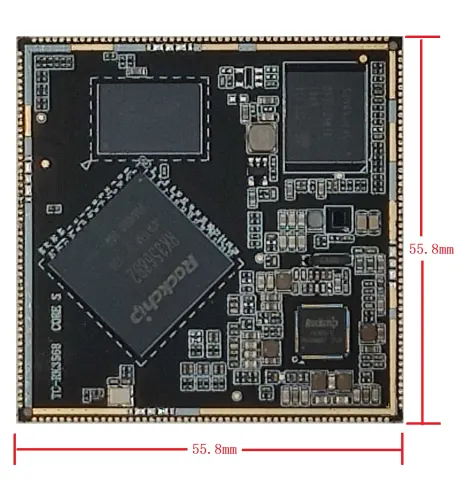

SOM Przód

|

SZPILKA |

Definicja pinów płyty głównej |

Funkcja domyślna |

Domyślny opis funkcji |

Moc wejścia/wyjścia |

Podkładka typu IO pull |

|

1 |

VCC3V3_SYS |

Zasilacz systemu 3,3 V |

Napięcie wejściowe 3,3 V |

|

- |

|

2 |

VCC3V3_SYS |

Zasilacz systemu 3,3 V |

Napięcie wejściowe 3,3 V |

|

- |

|

3 |

GND |

GND |

GND |

|

- |

|

4 |

GND |

GND |

GND |

|

- |

|

5 |

SDMMC0_DET_L |

SDMMC0_DET/SATA_CP_DET/PCIE30X1_CLKREQn_M0/GPIO0_A4_u |

SDMMC0 wykrywa wejście |

3,3 V |

I/O GÓRA |

|

6 |

SDMMC0_D3 |

SDMMC0_D3/ARMJTAG_TMS/UART5_RTSn_M0/GPIO2_A0_u |

Port danych SDMMC0 |

3,3 V |

I/O GÓRA

|

|

7 |

SDMMC0_D2 |

SDMMC0_D2/ARMJTAG_TCK/UART5_CTSn_M0/GPIO1_D7_u |

Port danych SDMMC0 |

3,3 V |

I/O GÓRA

|

|

8 |

SDMMC0_D1 |

SDMMC0_D1/UART2_RX_M1/UART6_RX_M1/PWM9_M1/GPIO1_D6_u |

Port danych SDMMC0 |

3,3 V |

I/O GÓRA

|

|

9 |

SDMMC0_D0 |

SDMMC0_D0/UART2_TX_M1/UART6_TX_M1/PWM8_M1/GPIO1_D5_u |

Port danych SDMMC0 |

3,3 V |

I/O GÓRA

|

|

10 |

SDMMC0_CMD |

SDMMC0_CMD/PWM10_M1/UART5_RX_M0/CAN0_TX_M1/GPIO2_A1_u |

Wyjście polecenia SDMMC0 |

3,3 V |

I/O GÓRA

|

|

11 |

SDMMC0_CLK |

SDMMC0_CLK/TEST_CLKOUT/UART5_TX_M0/CAN0_RX_M1/GPIO2_A2_d |

Wyjście zegara SDMMC0

|

3,3 V |

I/O W DÓŁ |

|

12 |

ZRESETOWAĆ |

NPOR_U |

Zresetuj wykrywanie sygnału |

3,3 V |

- |

|

13 |

RK809_PWRON |

Zasilanie włączone |

Włącz wejście sygnału, klucz zasilania połączenia zewnętrznego, aktywny niski |

|

- |

|

14 |

POWRÓT DO ZDROWIA |

SARADC_VIN0 |

Wejście z klawiatury AD |

1,8 V |

- |

|

15 |

EXT_EN |

EXT_EN |

Włączenie zasilania PMIC |

|

- |

|

16 |

HPR_OUT |

HPR_OUT |

Słuchawki od razu |

3,3 V |

- |

|

17 |

HPL_OUT |

HPL_OUT |

Słuchawki pominięte |

3,3 V |

- |

|

18 |

SPKP_OUT |

SPKP_OUT |

Mówić otwarcie |

5V/0,6W |

- |

|

19 |

SPKN_OUT |

SPKN_OUT |

Mówić otwarcie- |

5V/0,6W |

- |

|

20 |

MIC1_INN |

MIC1_INN/MIC_R |

MIC1_INN |

3,3 V |

- |

|

21 |

MIC1_INP |

MIC1_INP/MIC_L |

MIC1_INP |

3,3 V |

- |

|

22 |

HP_DET_L_GPIO3_C2 |

LCDC_VSYNC/VOP_BT1120_D14/SPI1_MISO_M1/UART5_TX_M1/I2S1_SDO3_M2/GPIO3_C2_d |

Wykrywanie słuchawek |

3,3 V |

I/O W DÓŁ |

|

23 |

SPK_CTL_H_GPIO3_C3 |

LCDC_DEN/VOP_BT1120_D15/SPI1_CLK_M1/UART5_RX_M1/I2S1_SCLK_RX_M2/GPIO3_C3_d |

|

3,3 V |

I/O W DÓŁ |

|

24 |

VCC3V3_SD |

Zasilanie 3,3 V |

Napięcie wyjściowe 3,3 V dla karty SD, znamionowy prąd wyjściowy 2A |

|

- |

|

25 |

VCC_3V3 |

Zasilanie 3,3 V |

Napięcie wyjściowe 3,3 V, znamionowy prąd wyjściowy 2 A |

|

- |

|

26 |

VCC_1V8 |

Zasilanie 1,8 V |

Napięcie wyjściowe 1,8 V, znamionowy prąd wyjściowy 2,5 A |

|

- |

|

27 |

PDM_SDI1_M0_ADC |

I2S1_SDO3_M0/I2S1_SDI1_M0/PDM_SDI1_M0/PCIE20_PERSTn_M2/GPIO1_B2_d |

PDM_SDI1_M0_ADC |

3,3 V |

IO W DÓŁ |

|

28 |

PDM_SDI2_M0_ADC |

I2S1_SDO2_M0/I2S1_SDI2_M0/PDM_SDI2_M0/PCIE20_WAKEn_M2/ACODEC_ADC_SYNC/GPIO1_B1_d |

PDM_SDI2_M0_ADC |

3,3 V |

IO W DÓŁ |

|

29 |

PDM_SDI3_M0_ADC |

I2S1_SDO1_M0/I2S1_SDI3_M0/PDM_SDI3_M0/PCIE20_CLKREQn_M2/ACODEC_DAC_DATAR/GPIO1_B0_d |

PDM_SDI3_M0_ADC |

3,3 V |

IO W DÓŁ |

|

30 |

PDM_CLK1_M0_ADC |

I2S1_SCLK_RX_M0/UART4_RX_M0/PDM_CLK1_M0/SPDIF_TX_M0/GPIO1_A4_d |

PDM_CLK1_M0_ADC |

3,3 V |

IO W DÓŁ |

|

31 |

GMAC0_TXD0 |

GMAC0_TXD0/UART1_RX_M0/GPIO2_B3_u |

GMAC0 przesyła dane |

1,8 V |

I/O GÓRA |

|

32 |

GMAC0_TXD1 |

GMAC0_TXD1/UART1_TX_M0/GPIO2_B4_u |

GMAC0 przesyła dane |

1,8 V |

I/O GÓRA |

|

33 |

GMAC0_TXD2 |

SDMMC1_D3/GMAC0_TXD2/UART7_TX_M0/GPIO2_A6_u |

GMAC0 przesyła dane |

1,8 V |

I/O GÓRA |

|

34 |

GMAC0_TXD3 |

SDMMC1_CMD/GMAC0_TXD3/UART9_RX_M0/GPIO2_A7_u |

GMAC0 przesyła dane |

1,8 V |

I/O GÓRA |

|

35 |

GMAC0_TXEN |

GMAC0_TXEN/UART1_RTSn_M0/SPI1_CLK_M0/GPIO2_B5_u |

Włączenie transmisji GMAC0 |

1,8 V |

I/O GÓRA |

|

36 |

GMAC0_TXCLK |

SDMMC1_CLK/GMAC0_TXCLK/UART9_TX_M0/GPIO2_B0_d |

Zegar transmisji GMAC0 |

1,8 V |

I/O W DÓŁ |

|

37 |

GMAC0_RXD0 |

GMAC0_RXD0/UART1_CTSn_M0/SPI1_MISO_M0/GPIO2_B6_u |

GMAC0 odbiera dane |

1,8 V |

I/O GÓRA |

|

38 |

GMAC0_RXD1 |

I2S2_SCLK_RX_M0/GMAC0_RXD1/UART6_RTSn_M0/SPI1_MOSI_M0/GPIO2_B7_d |

GMAC0 odbiera dane |

1,8 V |

I/O W DÓŁ |

|

39 |

GMAC0_RXD2 |

SDMMC1_D0/GMAC0_RXD2/UART6_RX_M0/GPIO2_A3_u |

GMAC0 odbiera dane |

1,8 V |

I/O GÓRA |

|

40 |

GMAC0_RXD3 |

SDMMC1_D1/GMAC0_RXD3/UART6_TX_M0/GPIO2_A4_u |

GMAC0 odbiera dane |

1,8 V |

I/O GÓRA |

|

41 |

GMAC0_RXDV_CRS |

I2S2_LRCK_RX_M0/GMAC0_RXDV_CRS/UART6_CTSn_M0/SPI1_CS0_M0/GPIO2_C0_d |

Prawidłowy sygnał danych GMAC0 RX |

1,8 V |

I/O W DÓŁ |

|

42 |

GMAC0_RXCLK |

SDMMC1_D2/GMAC0_RXCLK/UART7_RX_M0/GPIO2_A5_u |

Zegar odbioru GMAC0 |

1,8 V |

I/O GÓRA |

|

43 |

ETH0_REFCLKO_25M |

I2S2_MCLK_M0/ETH0_REFCLKO_25M/UART7_RTSn_M0/SPI2_CLK_M0/GPIO2_C1_d |

ETH0_REF CLOCK OUTPUT_25 MHz CPU do PHY, domyślnie NC |

1,8 V |

I/O W DÓŁ |

|

44 |

GMAC0_MCLKINOUT |

I2S2_SCLK_TX_M0/GMAC0_MCLKINOUT/UART7_CTSn_M0/SPI2_MISO_M0/GPIO2_C2_d |

Zewnętrzny zegar GMAC0 |

1,8 V |

I/O W DÓŁ |

|

45 |

GMAC0_MDC |

I2S2_LRCK_TX_M0/GMAC0_MDC/UART9_RTSn_M0/SPI2_MOSI_M0/GPIO2_C3_d |

Zegar zarządzający MAC0 |

1,8 V |

I/O W DÓŁ |

|

46 |

GMAC0_MDIO |

I2S2_SDO_M0/GMAC0_MDIO/UART9_CTSn_M0/SPI2_CS0_M0/GPIO2_C4_d |

Polecenie zarządzania MAC0 i dane |

1,8 V |

I/O W DÓŁ |

|

47 |

GMAC0_RSTN_GPIO3_B7 |

LCDC_D21/VOP_BT1120_D12/GMAC1_TXD1_M0/I2C3_SDA_M1/PWM11_IR_M0/GPIO3_B6_d |

|

3,3 V |

IO W DÓŁ |

|

48 |

GMAC0_INT_PMEB_GPIO3_C0 |

LCDC_HSYNC/VOP_BT1120_D13/SPI1_MOSI_M1/PCIE20_PERSTn_M1/I2S1_SDO2_M2/GPIO3_C1_d |

|

3,3 V |

I/O W DÓŁ |

|

49 |

RTCTC_INT_L_GPIO0_D3 |

GPIO0_D3_d |

RTC_IC_INT, aktywny niski |

1,8 V |

I/O W DÓŁ |

|

50 |

I2C5_SDA_M0 |

LCDC_D19/VOP_BT1120_D10/GMAC1_RXER_M0/I2C5_SDA_M0/PDM_SDI1_M2/GPIO3_B4_d |

Port szeregowy I2C 5 |

3,3 V |

I/O W DÓŁ |

|

51 |

I2C5_SCL_M0 |

LCDC_D18/VOP_BT1120_D9/GMAC1_RXDV_CRS_M0/I2C5_SCL_M0/PDM_SDI0_M2/GPIO3_B3_d |

Port szeregowy I2C 5 |

3,3 V |

I/O W DÓŁ |

|

52 |

PWM3_IR |

PWM3_IR/EDP_HPDIN_M1/PCIE30X1_WAKEn_M0/MCU_JTAG_TMS/GPIO0_C2_d |

|

3,3 V |

I/O W DÓŁ |

|

53 |

CAN1_TX_M1 |

PWM15_IR_M1/SPI3_MOSI_M1/CAN1_TX_M1/PCIE30X2_WAKEn_M2/I2S3_SCLK_M1/GPIO4_C3_d |

Transmisja danych CAN |

3,3 V |

I/O W DÓŁ |

|

54 |

CAN1_RX_M1 |

PWM14_M1/SPI3_CLK_M1/CAN1_RX_M1/PCIE30X2_CLKREQn_M2/I2S3_MCLK_M1/GPIO4_C2_d |

Odbiór danych CAN |

3,3 V |

I/O W DÓŁ |

|

55 |

UART2_RX_M0_DEBUG |

UART2_RX_M0/GPIO0_D0_u |

Port szeregowy UART |

3,3 V |

I/O GÓRA |

|

56 |

UART2_TX_M0_DEBUG |

UART2_TX_M0/GPIO0_D1_u |

Przesyłanie danych portu szeregowego UART w celu debugowania |

3,3 V |

I/O GÓRA |

|

57 |

UART3_RX_M1 |

LCDC_D23/PWM13_M0/GMAC1_MCLKINOUT_M0/UART3_RX_M1/PDM_SDI3_M2/GPIO3_C0_d |

Odbiór danych portu morskiego UART |

3,3 V |

I/O W DÓŁ |

|

58 |

UART3_TX_M1 |

LCDC_D22/PWM12_M0/GMAC1_TXEN_M0/UART3_TX_M1/PDM_SDI2_M2/GPIO3_B7_d |

Transmisja danych portu morskiego UART |

3,3 V |

I/O W DÓŁ |

|

59 |

UART4_TX_M1 |

LCDC_D17/VOP_BT1120_D8/GMAC1_RXD1_M0/UART4_TX_M1/PWM9_M0/GPIO3_B2_d |

Transmisja danych portu morskiego UART |

3,3 V |

I/O W DÓŁ |

|

60 |

UART4_RX_M1 |

LCDC_D16/VOP_BT1120_D7/GMAC1_RXD0_M0/UART4_RX_M1/PWM8_M0/GPIO3_B1_d |

Odbiór danych portu morskiego UART |

3,3 V |

I/O W DÓŁ |

|

61 |

UART9_RX_M1 |

PWM13_M1/SPI3_CS0_M1/SATA0_ACT_LED/UART9_RX_M1/I2S3_SDI_M1/GPIO4_C6_d |

Odbiór danych portu morskiego UART |

3,3 V |

I/O W DÓŁ |

|

62 |

UART9_TX_M1 |

PWM12_M1/SPI3_MISO_M1/SATA1_ACT_LED/UART9_TX_M1/I2S3_SDO_M1/GPIO4_C5_d |

Transmisja danych portu morskiego UART |

3,3 V |

I/O W DÓŁ |

|

63 |

UART7_RX_M1 |

PWM15_IR_M0/SPDIF_TX_M1/GMAC1_MDIO_M0/UART7_RX_M1/I2S1_LRCK_RX_M2/GPIO3_C5_d |

Odbiór danych portu morskiego UART |

3,3 V |

I/O W DÓŁ |

|

64 |

UART7_TX_M1 |

PWM14_M0/VOP_PWM_M1/GMAC1_MDC_M0/UART7_TX_M1/PDM_CLK1_M2/GPIO3_C4_d |

Transmisja danych portu morskiego UART |

3,3 V |

I/O W DÓŁ |

|

65 |

RS485_DIR_GPIO3_B5 |

LCDC_D20/VOP_BT1120_D11/GMAC1_TXD0_M0/I2C3_SCL_M1/PWM10_M0/GPIO3_B5_d |

Kierunek danych RS485 |

3,3 V |

I/O W DÓŁ |

|

66 |

DVP_PWREN0_H_GPIO0_B0 |

CLK32K_IN/CLK32K_OUT0/PCIE30X2_BUTTONRSTn/GPIO0_B0_u |

|

3,3 V |

I/O GÓRA |

|

67 |

WIFI_PWREN_L_GPIO0_C1 |

PWM2_M0/NPUAVS/UART0_TX/MCU_JTAG_TDI/GPIO0_C1_d |

|

3,3 V |

I/O W DÓŁ |

|

68 |

I2S3_SDI_M0 |

LCDC_D13/VOP_BT1120_CLK/GMAC1_TXCLK_M0/I2S3_SDI_M0/SDMMC2_CLK_M1/GPIO3_A6_d |

I2S3_SDI |

3,3 V |

I/O W DÓŁ |

|

69 |

I2S3_SDO_M0 |

LCDC_D12/VOP_BT1120_D4/GMAC1_RXD3_M0/I2S3_SDO_M0/SDMMC2_CMD_M1/GPIO3_A5_d |

I2S3_SDO |

3,3 V |

I/O W DÓŁ |

|

70 |

I2S3_LRCK_M0 |

LCDC_D11/VOP_BT1120_D3/GMAC1_RXD2_M0/I2S3_LRCK_M0/SDMMC2_D3_M1/GPIO3_A4_d |

I2S3_LRCK |

3,3 V |

I/O W DÓŁ |

|

71 |

I2S3_SCLK_M0 |

LCDC_D10/VOP_BT1120_D2/GMAC1_TXD3_M0/I2S3_SCLK_M0/SDMMC2_D2_M1/GPIO3_A3_d |

I2S3_SCLK |

3,3 V |

I/O W DÓŁ |

|

72 |

HOST_WAKE_BT_H_GPIO3_A2 |

LCDC_D9/VOP_BT1120_D1/GMAC1_TXD2_M0/I2S3_MCLK_M0/SDMMC2_D1_M1/GPIO3_A2_d |

HOST_WAKE_BT |

3,3 V |

I/O W DÓŁ |

|

73 |

BT_WAKE_HOST_H_GPIO3_A1 |

LCDC_D8/VOP_BT1120_D0/SPI1_CS0_M1/PCIE30X1_PERSTn_M1/SDMMC2_D0_M1/GPIO3_A1_d |

BT_WAKE_HOST |

3,3 V |

I/O W DÓŁ |

|

74 |

BT_REG_ON_H_GPIO3_A0 |

LCDC_CLK/VOP_BT656_CLK_M0/SPI2_CLK_M1/UART8_RX_M1/I2S1_SDO1_M2/GPIO3_A0_d |

Włączenie zasilania modułu Bluetooth |

3,3 V |

I/O W DÓŁ |

|

75 |

UART8_RX_M0 |

CLK32K_OUT1/UART8_RX_M0/SPI1_CS1_M0/GPIO2_C6_d |

Odbiór danych portu morskiego UART |

1,8V |

I/O W DÓŁ |

|

76 |

UART8_TX_M0 |

I2S2_SDI_M0/GMAC0_RXER/UART8_TX_M0/SPI2_CS1_M0/GPIO2_C5_d |

Transmisja danych portu morskiego UART |

1,8 V |

I/O W DÓŁ |

|

77 |

UART8_CTSN_M0 |

SDMMC1_DET/I2C4_SCL_M1/UART8_CTSn_M0/CAN2_TX_M1/GPIO2_B2_u |

UART8_CTSn_M0 |

1,8 V |

I/O W DÓŁ |

|

78 |

UART8_RTSN_M0 |

SDMMC1_PWREN/I2C4_SDA_M1/UART8_RTSn_M0/CAN2_RX_M1/GPIO2_B1_d |

UART8_RTSn_M0 |

1,8 V |

I/O W DÓŁ |

|

79 |

WIFI_REG_ON_H_GPIO3_D5 |

CIF_D7/EBC_SDDO7/SDMMC2_PWREN_M0/I2S1_SDI3_M1/VOP_BT656_D7_M1/GPIO3_D5_d |

Włącz WIFI_REG |

1,8 V |

I/O W DÓŁ |

|

80 |

WIFI_WAKE_HOST_H_GPIO3_D4 |

CIF_D6/EBC_SDDO6/SDMMC2_DET_M0/I2S1_SDI2_M1/VOP_BT656_D6_M1/GPIO3_D4_d |

Gospodarz budzenia WIFI |

1,8 V |

I/O W DÓŁ |

|

81 |

SDMMC2_CLK_M0 |

CIF_D5/EBC_SDDO5/SDMMC2_CLK_M0/I2S1_SDI1_M1/VOP_BT656_D5_M1/GPIO3_D3_d |

Zegar SDMMC2 |

1,8 V |

I/O W DÓŁ |

|

82 |

SDMMC2_CMD_M0 |

CIF_D4/EBC_SDDO4/SDMMC2_CMD_M0/I2S1_SDI0_M1/VOP_BT656_D4_M1/GPIO3_D2_d |

Polecenie SDMMC2 |

1,8 V |

I/O W DÓŁ |

|

83 |

SDMMC2_D3_M0 |

CIF_D3/EBC_SDDO3/SDMMC2_D3_M0/I2S1_SDO0_M1/VOP_BT656_D3_M1/GPIO3_D1_d |

Dane SDMMC2 |

1,8 V |

I/O W DÓŁ |

|

84 |

SDMMC2_D2_M0 |

CIF_D2/EBC_SDDO2/SDMMC2_D2_M0/I2S1_LRCK_TX_M1/VOP_BT656_D2_M1/GPIO3_D0_d |

Dane SDMMC2 |

1,8 V |

I/O W DÓŁ |

|

85 |

SDMMC2_D1_M0 |

CIF_D1/EBC_SDDO1/SDMMC2_D1_M0/I2S1_SCLK_TX_M1/VOP_BT656_D1_M1/GPIO3_C7_d |

Dane SDMMC2 |

1,8 V |

I/O W DÓŁ |

|

86 |

SDMMC2_D0_M0 |

CIF_D0/EBC_SDDO0/SDMMC2_D0_M0/I2S1_MCLK_M1/VOP_BT656_D0_M1/GPIO3_C6_d |

Dane SDMMC2 |

1,8 V |

I/O W DÓŁ |

|

87 |

GMAC1_INT/PMEB_GPIO3_A7 |

LCDC_D14/VOP_BT1120_D5/GMAC1_RXCLK_M0/SDMMC2_DET_M1/GPIO3_A7_d |

|

3,3 V |

I/O W DÓŁ |

|

88 |

GMAC1_RSTN_GPIO3_B0 |

LCDC_D15/VOP_BT1120_D6/ETH1_REFCLKO_25M_M0/SDMMC2_PWREN_M1/GPIO3_B0_d |

|

3,3 V |

I/O W DÓŁ |

|

89 |

GMAC1_MDIO_M1 |

IF_VSYNC/EBC_SDOE/GMAC1_MDIO_M1/I2S2_SCLK_TX_M1/GPIO4_B7_d |

Komenda i dane zarządzania GMAC1 |

1,8 V |

I/O W DÓŁ |

|

90 |

GMAC1_MDC_M1 |

CIF_HREF/EBC_SDLE/GMAC1_MDC_M1/UART1_RTSn_M1/I2S2_MCLK_M1/GPIO4_B6_d |

Zegar zarządzający GMAC1 |

1,8 V |

I/O W DÓŁ |

|

91 |

GMAC1_MCLKINOUT_M1 |

CIF_CLKIN/EBC_SDCLK/GMAC1_MCLKINOUT_M1/UART1_CTSn_M1/I2S2_SCLK_RX_M1/GPIO4_C1_d |

Zewnętrzny zegar GMAC1 |

1,8 V |

I/O W DÓŁ |

|

92 |

ETH1_REFCLKO_25M_M1 |

I2C4_SCL_M0/EBC_GDOE/ETH1_REFCLKO_25M_M1/SPI3_CLK_M0/I2S2_SDO_M1/GPIO4_B3_d |

ETH1 Wyjście zegarowe |

1,8 V |

I/O W DÓŁ |

|

93 |

GMAC1_RXCLK_M1 |

CIF_D13/EBC_SDDO13/GMAC1_RXCLK_M1/UART7_RX_M2/PDM_SDI3_M1/GPIO4_A3_d |

Zegar odbioru GMAC1 |

1,8 V |

I/O W DÓŁ |

|

94 |

GMAC1_RXDV_CRS_M1 |

ISP_PRELIGHT_TRIG/EBC_SDCE3/GMAC1_RXDV_CRS_M1/I2S1_SDO2_M1/GPIO4_B1_d |

Prawidłowy sygnał danych GMAC1 RX |

1,8 V |

I/O W DÓŁ |

|

95 |

GMAC1_RXD3_M1 |

CIF_D12/EBC_SDDO12/GMAC1_RXD3_M1/UART7_TX_M2/PDM_SDI2_M1/GPIO4_A2_d |

GMAC1 odbiera dane |

1,8 V |

I/O W DÓŁ |

|

96 |

GMAC1_RXD2_M1 |

CIF_D11/EBC_SDDO11/GMAC1_RXD2_M1/PDM_SDI1_M1/GPIO4_A1_d |

GMAC1 odbiera dane |

1,8 V |

I/O W DÓŁ |

|

97 |

GMAC1_RXD1_M1 |

CAM_CLKOUT1/EBC_SDCE2/GMAC1_RXD1_M1/SPI3_MISO_M0/I2S1_SDO1_M1/GPIO4_B0_d |

GMAC1 odbiera dane |

1,8 V |

I/O W DÓŁ |

|

98 |

GMAC1_RXD0_M1 |

CAM_CLKOUT0/EBC_SDCE1/GMAC1_RXD0_M1/SPI3_CS1_M0/I2S1_LRCK_RX_M1/GPIO4_A7_d |

GMAC1 odbiera dane |

1,8 V |

I/O W DÓŁ |

|

99 |

GMAC1_TXCLK_M1 |

CIF_D10/EBC_SDDO10/GMAC1_TXCLK_M1/PDM_CLK1_M1/GPIO4_A0_d |

Zegar transmisji GMAC1 |

1,8 V |

I/O W DÓŁ |

|

100 |

GMAC1_TXEN_M1 |

ISP_FLASHTRIGOUT/EBC_SDCE0/GMAC1_TXEN_M1/SPI3_CS0_M0/I2S1_SCLK_RX_M1/GPIO4_A6_d |

Włączenie transmisji GMAC1 |

1,8 V |

I/O W DÓŁ |

|

101 |

GMAC1_TXD3_M1 |

CIF_D9/EBC_SDDO9/GMAC1_TXD3_M1/UART1_RX_M1/PDM_SDI0_M1/GPIO3_D7_d |

GMAC1 przesyła dane |

1,8 V |

I/O W DÓŁ |

|

102 |

GMAC1_TXD2_M1 |

CIF_D8/EBC_SDDO8/GMAC1_TXD2_M1/UART1_TX_M1/PDM_CLK0_M1/GPIO3_D6_d |

GMAC1 przesyła dane |

1,8 V |

I/O W DÓŁ |

|

103 |

GMAC1_TXD1_M1 |

CIF_D15/EBC_SDDO15/GMAC1_TXD1_M1/UART9_RX_M2/I2S2_LRCK_RX_M1/GPIO4_A5_d |

GMAC1 przesyła dane |

1,8 V |

I/O W DÓŁ |

|

104 |

GMAC1_TXD0_M1 |

CIF_D14/EBC_SDDO14/GMAC1_TXD0_M1/UART9_TX_M2/I2S2_LRCK_TX_M1/GPIO4_A4_d |

GMAC1 przesyła dane |

1,8 V |

I/O W DÓŁ |

|

105 |

TP_RST_L_GPIO0_B6 |

I2C2_SDA_M0/SPI0_MOSI_M0/PCIE20_PERSTn_M0/PWM2_M1/GPIO0_B6_u |

Resetowanie panelu dotykowego |

3,3 V |

I/O GÓRA

|

|

106 |

TP_INT_L_GPIO0_B5 |

I2C2_SCL_M0/SPI0_CLK_M0/PCIE20_WAKEn_M0/PWM1_M1/GPIO0_B5_u |

Wprowadzanie danych przerwania panelu dotykowego |

3,3 V |

I/O GÓRA |

|

107 |

I2C1_SDA_TP |

I2C1_SDA/CAN0_RX_M0/PCIE20_BUTTONRSTn/MCU_JTAG_TCK/GPIO0_B4_u |

Port szeregowy I2C 1 |

3,3 V |

I/O GÓRA |

|

108 |

I2C1_SCL_TP |

I2C1_SCL/CAN0_TX_M0/PCIE30X1_BUTTONRSTn/MCU_JTAG_TDO/GPIO0_B3_u |

Port szeregowy I2C 1 |

3,3 V |

I/O GÓRA |

|

109 |

I2C3_SCL_M0 |

I2C3_SCL_M0/UART3_TX_M0/CAN1_TX_M0/AUDIOPWM_LOUT_N/ACODEC_ADC_CLK/GPIO1_A1_u |

Port szeregowy I2C 3 |

3,3 V |

I/O GÓRA |

|

110 |

I2C3_SDA_M0 |

I2C3_SDA_M0/UART3_RX_M0/CAN1_RX_M0/AUDIOPWM_LOUT_P/ACODEC_ADC_DATA/GPIO1_A0_u |

Port szeregowy I2C 3 |

3,3 V |

I/O GÓRA |

|

111 |

I2C2_SCL_M1 |

I2C2_SCL_M1/EBC_SDSHR/CAN2_TX_M0/I2S1_SDO3_M1/GPIO4_B5_d |

Port szeregowy I2C 2 |

1,8 V |

I/O W DÓŁ |

|

112 |

I2C2_SDA_M1 |

I2C2_SDA_M1/EBC_GDSP/CAN2_RX_M0/ISP_FLASH_TRIGIN/VOP_BT656_CLK_M1/GPIO4_B4_d |

Port szeregowy I2C 2 |

1,8 V |

I/O W DÓŁ |

|

113 |

MIPI_CAM1_PDN_L_GPIO3_D3 |

LCDC_D1/VOP_BT656_D1_M0/SPI0_MOSI_M1/PCIE20_WAKEn_M1/I2S1_SCLK_TX_M2/GPIO2_D1_d |

Wyłączenie aparatu1 |

3,3 V |

I/O W DÓŁ |

|

114 |

MIPI_CAM1_RST_L_GPIO3_D2 |

LCDC_D0/VOP_BT656_D0_M0/SPI0_MISO_M1/PCIE20_CLKREQn_M1/I2S1_MCLK_M2/GPIO2_D0_d |

Reset aparatu1 |

3,3 V |

I/O W DÓŁ |

|

115 |

MIPI_CAM0_RST_L_GPIO3_D4 |

LCDC_D2/VOP_BT656_D2_M0/SPI0_CS0_M1/PCIE30X1_CLKREQn_M1/I2S1_LRCK_TX_M2/GPIO2_D2_d |

Reset aparatu0 |

3,3 V |

I/O W DÓŁ |

|

116 |

MIPI_CAM0_PDN_L_GPIO3_D5 |

LCDC_D3/VOP_BT656_D3_M0/SPI0_CLK_M1/PCIE30X1_WAKEn_M1/I2S1_SDI0_M2/GPIO2_D3_d |

Aparat 0 wyłączony |

3,3 V |

I/O W DÓŁ |

|

117 |

USB2_HOST2_DM |

USB2_HOST2_DM |

USB2_HOST2_DM |

3,3 V |

- |

|

118 |

USB2_HOST2_DP |

USB2_HOST2_DP |

USB2_HOST2_DP |

3,3 V |

- |

|

119 |

USB2_HOST3_DM |

USB2_HOST3_DM |

USB2_HOST3_DM |

3,3 V |

- |

|

120 |

USB2_HOST3_DP |

USB2_HOST3_DP |

USB2_HOST3_DP |

3,3 V |

- |

|

121 |

REFCLK_OUT |

REFCLK_OUT/GPIO0_A0_d |

Wyjście zegara dla kamery |

3,3 V |

I/O W DÓŁ |

|

122 |

CIF_CLKOUT |

CIF_CLKOUT/EBC_GDCLK/PWM11_IR_M1/GPIO4_C0_d |

Koniec zegara CIF |

1,8 V |

I/O W DÓŁ |

|

123 |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

1,8 V |

- |

|

124 |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

1,8 V |

- |

|

125 |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

1,8 V |

- |

|

126 |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

1,8 V |

- |

|

127 |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

1,8 V |

- |

|

128 |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

1,8 V |

- |

|

129 |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

1,8 V |

- |

|

130 |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

1,8 V |

- |

|

131 |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

1,8 V |

- |

|

132 |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

1,8 V |

- |

|

133 |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

1,8 V |

- |

|

134 |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

1,8 V |

- |

|

135 |

LCD1_PWREN_H_GPIO0_C5 |

PWM6/SPI0_MISO_M0/PCIE30X2_WAKEn_M0/GPIO0_C5_d |

Włączenie zasilania wyświetlacza LCD |

3,3 V |

I/O W DÓŁ |

|

136 |

LCD1_BL_PWM5 |

PWM5/SPI0_CS1_M0/UART0_RTSn/GPIO0_C4_d |

Podświetlenie LCD PWM |

3,3 V |

I/O W DÓŁ |

|

137 |

LCD1_BL_PWM4 |

PWM4/VOP_PWM_M0/PCIE30X1_PERSTn_M0/MCU_JTAG_TRSTn/GPIO0_C3_d |

Podświetlenie LCD PWM |

3,3 V |

I/O W DÓŁ |

|

138 |

LCD0_PWREN_H_GPIO0_C7 |

HDMITX_CEC_M1/PWM0_M1/UART0_CTSn/GPIO0_C7_d |

Włączenie zasilania wyświetlacza LCD |

3,3 V |

I/O W DÓŁ |

|

139 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

1,8 V |

- |

|

140 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

1,8 V |

- |

|

141 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

1,8 V |

- |

|

142 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

1,8 V |

- |

|

143 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

1,8 V |

- |

|

144 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

1,8 V |

- |

|

145 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

1,8 V |

- |

|

146 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

1,8 V |

- |

|

147 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

1,8 V |

- |

|

148 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

1,8 V |

- |

|

149 |

HDMI_TXCLKN_PORT |

HDMI_TX_CLKN |

HDMI_TX2CLKN_PORT i rezystancja szeregowa 2.2R |

1,8 V |

- |

|

150 |

HDMI_TXCLKP_PORT |

HDMI_TX_CLKP |

HDMI_TXCLKP_PORT i rezystancja szeregowa 2.2R |

1,8 V |

- |

|

151 |

HDMI_TX0N_PORT |

HDMI_TX_D0N |

HDMI_TX0N_PORT i rezystancja szeregowa 2.2R |

1,8 V |

- |

|

152 |

HDMI_TX0P_PORT |

HDMI_TX_D0P |

HDMI_TX0P_PORT i rezystancja szeregowa 2.2R |

1,8 V |

- |

|

153 |

HDMI_TX1N_PORT |

HDMI_TX_D1N |

HDMI_TX1N_PORT i rezystancja szeregowa 2.2R |

1,8 V |

- |

|

154 |

HDMI_TX1P_PORT |

HDMI_TX_D1P |

HDMI_TX1P_PORT i rezystancja szeregowa 2.2R |

1,8 V |

- |

|

155 |

HDMI_TX2N_PORT |

HDMI_TX_D2N |

HDMI_TX2N_PORT i rezystancja szeregowa 2.2R |

1,8 V |

- |

|

156 |

HDMI_TX2P_PORT |

HDMI_TX_D2P |

HDMI_TX2P_PORT i rezystancja szeregowa 2.2R |

1,8 V |

- |

|

157 |

HDMITX_SCL |

HDMITX_SCL/I2C5_SCL_M1/GPIO4_C7_u |

Port szeregowy I2C dla HDMI |

3,3 V |

I/O GÓRA |

|

158 |

HDMITC_SDA |

HDMITX_SDA/I2C5_SDA_M1/GPIO4_D0_u |

Port szeregowy I2C dla HDMI |

3,3 V |

I/O GÓRA |

|

159 |

HDMITX_CEC_M0 |

HDMITX_CEC_M0/SPI3_CS1_M1/GPIO4_D1_u |

HDMITX_CEC |

3,3 V |

I/O GÓRA |

|

160 |

HDMI_TX_HPDIN |

HDMI_TX_HPDIN |

Hot plug HDMI_TX |

1,8 V |

- |

|

161 |

PCIE30X2_CLKREQN_M1 |

LCDC_D4/VOP_BT656_D4_M0/SPI2_CS1_M1/PCIE30X2_CLKREQn_M1/I2S1_SDI1_M2/GPIO2_D4_d |

PCIE30X2_CLKREQn |

3.3 |

I/O W DÓŁ |

|

162 |

PCIE30X2_WAKEN_M1 |

LCDC_D5/VOP_BT656_D5_M0/SPI2_CS0_M1/PCIE30X2_WAKEn_M1/I2S1_SDI2_M2/GPIO2_D5_d |

PCIE30X2_WAKEn |

3,3 V |

I/O W DÓŁ |

|

163 |

PCIE30X2_PERSTN_M1 |

LCDC_D6/VOP_BT656_D6_M0/SPI2_MOSI_M1/PCIE30X2_PERSTn_M1/I2S1_SDI3_M2/GPIO2_D6_d |

Zresetuj PCIE30X2 |

3,3 V |

I/O W DÓŁ |

|

164 |

PCIE30X2_PRSNT_L_GPIO2_D7 |

LCDC_D7/VOP_BT656_D7_M0/SPI2_MISO_M1/UART8_TX_M1/I2S1_SDO0_M2/GPIO2_D7_d |

Host wznawiania PCIE30X2 |

3,3 V |

I/O W DÓŁ |

|

165 |

PCIE_PWREN_H_GPIO0_D4 |

GPIO0_D4_d |

Włączenie zasilania PCIE |

1,8 V |

I/O W DÓŁ |

|

166 |

PCIE30_RX1N |

PCIE30_RX1N |

PCIE30_RX1N |

1,8 V |

- |

|

167 |

PCIE30_RX1P |

PCIE30_RX1P |

PCIE30_RX1P |

1,8 V |

- |

|

168 |

PCIE30_RX0N |

PCIE30_RX0N |

PCIE30_RX0N |

1,8 V |

- |

|

169 |

PCIE30_RX0P |

PCIE30_RX0P |

PCIE30_RX0P |

1,8 V |

- |

|

170 |

PCIE30_TX1N |

PCIE30_TX1N |

PCIE30_TX1N |

1,8 V |

- |

|

171 |

PCIE30_TX1P |

PCIE30_TX1P |

PCIE30_TX1P |

1,8 V |

- |

|

172 |

PCIE30_TX0N |

PCIE30_TX0N |

PCIE30_TX0N |

1,8 V |

- |

|

173 |

PCIE30_TX0P |

PCIE30_TX0P |

PCIE30_TX0P |

1,8 V |

- |

|

174 |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

1,8 V |

- |

|

175 |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

1,8 V |

- |

|

176 |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

1,8 V |

- |

|

177 |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

1,8 V |

- |

|

178 |

SATA2_RXN |

PCIE20_RXN/SATA2_RXN/QSGMII_RXN_M1 |

SATA2_RXN |

1,8 V |

- |

|

179 |

SATA2_RXP |

PCIE20_RXP/SATA2_RXP/QSGMII_RXP_M1 |

SATA2_RXP |

1,8 V |

- |

|

180 |

SATA2_TXN |

PCIE20_TXN/SATA2_TXN/QSGMII_TXN_M1 |

SATA2_TXN |

1,8 V |

- |

|

181 |

SATA2_TXP |

PCIE20_TXP/SATA2_TXP/QSGMII_TXP_M1 |

SATA2_TXP |

1,8 V |

- |

|

182 |

SATA2_ACT_LED |

EDP_HPDIN_M0/SPDIF_TX_M2/SATA2_ACT_LED/PCIE30X2_PERSTn_M2/I2S3_LRCK_M1/GPIO4_C4_d |

Wskazuje aktywność SATA |

3,3 V |

I/O W DÓŁ |

|

183 |

USB3_HOST1_SSTXP |

USB3_HOST1_SSTXP/SATA1_TXP/QSGMII_TXP_M0 |

USB3_HOST1_SSTXP |

1,8 V |

- |

|

184 |

USB3_HOST1_SSTXN |

USB3_HOST1_SSTXN/SATA1_TXN/QSGMII_TXN_M0 |

USB3_HOST1_SSTXN |

1,8 V |

- |

|

185 |

USB3_HOST1_SSRXP |

USB3_HOST1_SSRXP/SATA1_RXP/QSGMII_RXP_M0 |

USB3_HOST1_SSRXP |

1,8 V |

- |

|

186 |

USB3_HOST1_SSRXN |

USB3_HOST1_SSRXN/SATA1_RXN/QSGMII_RXN_M0 |

USB3_HOST1_SSRXN |

1,8 V |

- |

|

187 |

USB3_HOST1_DM |

USB3_HOST1_DM |

USB3_HOST1_DM |

3,3 V |

- |

|

188 |

USB3_HOST1_DP |

USB3_HOST1_DP |

USB3_HOST1_DP |

3,3 V |

- |

|

189 |

USB3_OTG0_SSTXP |

USB3_OTG0_SSTXP/SATA0_TXP |

USB3_OTG0_SSTXP |

1,8 V |

- |

|

190 |

USB3_OTG0_SSTXN |

USB3_OTG0_SSTXN/SATA0_TXN |

USB3_OTG0_SSTXN |

1,8 V |

- |

|

191 |

USB3_OTG0_SSRXP |

USB3_OTG0_SSRXP/SATA0_RXP |

USB3_OTG0_SSRXP |

1,8 V |

- |

|

192 |

USB3_OTG0_SSRXN |

USB3_OTG0_SSRXN/SATA0_RXN |

USB3_OTG0_SSRXN |

1,8 V |

- |

|

193 |

USB3_OTG0_DM |

USB3_OTG0_DM |

USB3_OTG0_DM |

3,3 V |

- |

|

194 |

USB3_OTG0_DP |

USB3_OTG0_DP |

USB3_OTG0_DP |

3,3 V |

- |

|

195 |

USB3_OTG0_ID |

USB3_OTG0_ID |

USB3_OTG0_ID |

3,3 V |

- |

|

196 |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUSDET |

Wykrywanie USB3_OTG0_VBUS |

3,3 V |

- |

|

197 |

USB_HOST_PWREN_H_GPIO0_A6 |

GPU_PWREN/SATA_CP_POD/PCIE30X2_CLKREQn_M0/GPIO0_A6_d |

Włączenie zasilania hosta USB |

3,3 V |

I/O W DÓŁ |

|

198 |

USB_OTG_PWREN_H_GPIO0_A5 |

SDMMC0_PWREN/SATA_MP_SWITCH/PCIE20_CLKREQn_M0/GPIO0_A5_d |

Włączenie zasilania USB OTG |

3,3 V |

I/O W DÓŁ |

|

199 |

DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

1,8 V |

- |

|

200 |

DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

1,8 V |

- |

|

201 |

DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

1,8 V |

- |

|

202 |

DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

1,8 V |

- |

|

203 |

DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

1,8 V |

- |

|

204 |

DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

1,8 V |

- |

|

205 |

DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

1,8 V |

- |

|

206 |

DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

1,8 V |

- |

|

207 |

DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

1,8 V |

- |

|

208 |

DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

1,8 V |

- |

Rozmiar to 150mm * 110mm, 4 warstwy, grubość 1.6mm.

|

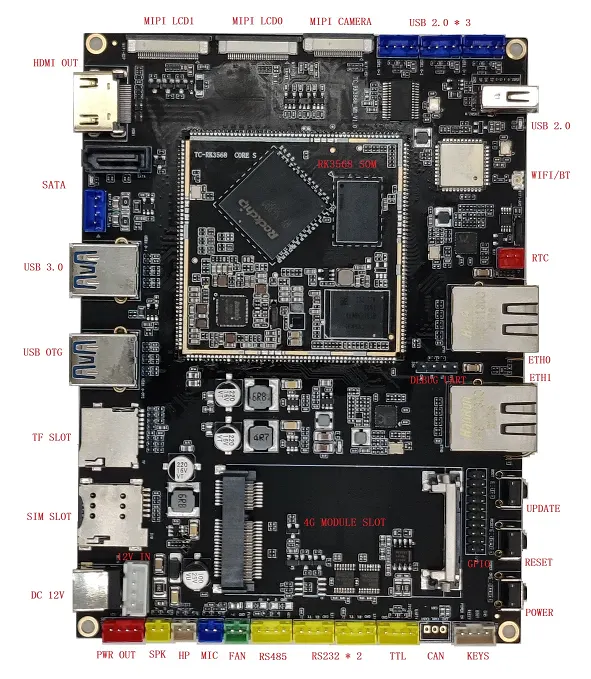

Opis interfejsów |

|

|

NIE. |

Imię |

|

ã1ã |

Wejście DC 12 V/4-stykowe wejście 12 V 2,54 mm |

|

ã2ã |

Gniazdo karty sim modułu 4G |

|

ã3ã |

Gniazdo karty TF |

|

ã4ã |

USB OTG |

|

ã5ã |

HOST USB3.0 |

|

ã6ã |

Dane SATA |

|

ã7ã |

Wyjście HDMI |

|

ã8ã |

MIPI LCD1 |

|

ã9ã |

MIPI LCD0 |

|

ã10ã |

Kamera MIPI |

|

ã11ã |

USB2.0 * 3 |

|

ã12ã |

USB2.0 typu A |

|

ã13ã |

WIFI/BT(AP6335) |

|

ã14ã |

RTC |

|

ã15ã |

ETH0 |

|

ã16ã |

ETH1 |

|

ã17ã |

Zaktualizuj klucz |

|

ã18ã |

Przycisk reset |

|

ã19ã |

Przycisk zasilania |

|

ã20ã |

Klucze (4pin 2.0mm) |

|

ã21ã |

MOŻE (3 piny 2,0 mm) |

|

ã22ã |

Uart TTL (4pin 2.0mm) |

|

ã23ã |

RS232 * 2 (4 piny 2.0mm) |

|

ã24ã |

RS485 (4 piny 2,0 mm) |

|

ã25ã |

WENTYLATOR (2 piny 2,0 mm) |

|

ã26ã |

MIKROFON (2 piny 2,0 mm) |

|

ã27ã |

HP (2pin 2.0mm) |

|

ã28ã |

SPK (2pin 2.0mm) |

|

ã29ã |

Wyjście zasilania (4pin 2.0mm) |

|

ã30ã |

Debuguj Uart (4pin 2.0mm) |

|

ã31ã |

GPIO(2*10pin 2,0mm) |

|

ã32ã |

Gniazdo modułu 4G (port PCIE) |

|

ã33ã |

RK3568 SOM |

Płyta wykorzystuje zasilacz 12 V DC, który można podłączyć za pomocą złącza wejściowego DC 12 V lub złącza wejściowego 4-pinowego 2,54 mm 12 V.

Szczegóły innych interfejsów mogą odnosić się do schematu i układu płytki rozwojowej.

Weź płytkę rozwojową TC-RK3568 jako platformę sprzętową, możesz odnieść się do projektu zasilania, projektu USB, projektu portu PCIE, projektu wyświetlacza MIPI, projektu audio, projektu Ethernet, projektu kamery i tak dalej. Są one otwarte dla klientów, mogą odnosić się do naszego projektu płyty nośnej.

Platforma programistyczna TC-RK3568 obsługuje systemy operacyjne Android11, Linux Buildroot, Ubuntu i Debian, kody źródłowe są otwarte. Możesz przeczytać odniesienia, takie jak instrukcja obsługi systemu Thinkcore TC-RK3568.